.

.

طراحی اسنابر مقاومت – خازن

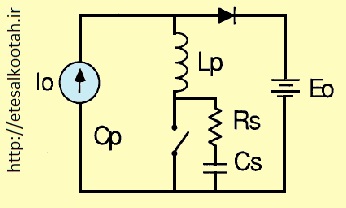

اسنابر مقاومت – خازن یا «اسنابر RC»، که مانند شکل 4 بر دو سر کلید قرار داده میشود، میتواند برای پایین آوردن قلهی ولتاژ در زمان قطع، و برای خفهکردن حالت نوسانی آن مورد استفاده قرار گیرد.

.

.

در اغلب حالتها، فوت و فنهای طراحی بسیار سادهای به کار برده میشوند تا مقدارهای مناسب برای اجزای اسنابر (Rs و Cs) تعیین شوند. در حالاتی که طراحی بهینهتری مورد نظر باشد، روند طراحیِ پیچیدهتری به کار برده میشود.

.

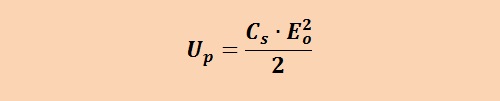

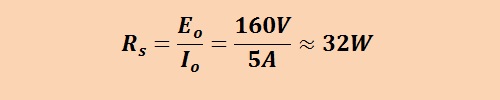

طراحی سریع اسنابر: برای دستیافتن به تضعیف شدید دامنه، باید شرط Cs > Cp برقرار باشد. یکی از اولین انتخابهای خوب، در نظر گرفتن دو برابر مجموع ظرفیت خازنی خروجیِ کلید و مقدار تخمینیِ ظرفیتهای خازنی ناشی از مونتاژ مدار است. Rs طوری انتخاب میشود که رابطهی Rs = Eo / Io برقرار باشد. این رابطه به معنی آن است که سهم ولتاژ داخلی ناشی از جریانی که از Rs عبور میکند، بزرگتر از ولتاژ محدود شدهی خروجی باشد. توان تلفاتی در Rs را میتوان از روی مقدار قلهایِ انرژیِ ذخیرهشده در خازن Cs به دست آورد:

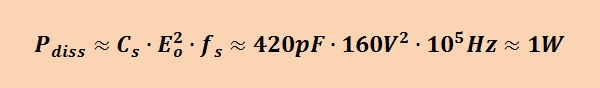

مقدار بالا انرژی تلفاتی در Rs است، هنگامی که خازن Cs شارژ و دشارژ شده باشد، طوری که میانگین توان تلفاتی در فرکانس کلیدگری (fs) برابر باشد با:

بسته به مقدار نوسانهای میرنده (رینگینگ[1])، توان تلفاتی واقعی ممکن است کمی بیشتر از مقدار بالا باشد.

مثالهای زیر چگونگی استفاده از این روش را نشان میدهند.

فرض کنیم که کلید ما یک ترانزیستور ماسفت از نوع IRF740 باشد که در آن Io = 5A و Eo = 160V است. در این افزاره ظرفیت خازنی خروجی Coss = 170pF است و ظرفیت مونتاژ در حدود 40 پیکوفاراد خواهد بود.

با دو برابر کردن جمع این دو ظرفیت، به مقدار 420 پیکوفاراد می رسیم. هر اسنابر 500 ولتی با ظرفیتی میان 390 تا 470 پیکوفاراد برای حفاظت از این ماسفت مناسب خواهد بود. ما مقدار نزدیکتر به مقدار محاسبه را انتخاب میکنیم. بنابراین داریم Co = 390pF . بیشینهی توان تلف شونده در مقاومت اسنابر برابر است با:

برای فرکانس کار 100 کیلوهرتزی، توان تلفاتی برابر است با Pdiss = 1W زیرا:

با در نظر گرفتن ضریب اطمینان، برای این جا از یک مقاومت 2 واتی استفاده خواهد شد. بهترین مقاومتها در این کاربرد، «مقاومتهای ترکیبی کربنی[2]» هستند چون این مقاومتها در مقایسه با «مقاومتهای لایهی نازک[3]» و یا «مقاومتهای سیمی[4]» دارای «اندوکتانس داخلی[5]» بسیار ناچیزی هستند. به کار بردن «مقاومتهای لایهی کربن[6]» هم تا جایی که برای تصحیح مقدار اهمی برشهای مارپیچی روی آنها انجام نشده باشد، در اسنابرها مجاز است.

در صورتی که این روش آسان و عملی نتواند قلههای ولتاژی را به شکل رضایتبخش محدود کند، یا باید ظرفیت خازن اسنابر را بالاتر برد و یا از روش بهینهسازی استفاده نمود.

.

اسنابر مقاومت – خازن بهینه شده: در حالاتی که باید قلههای ولتاژی به کمینهی مقدار رسانده شده و همزمان در مورد توان تلفاتی نگرانی وجود داشته باشد، بایستی از روند طراحی بهتری استفاده گردد. در یک مقالهی علمی معتبر از «دکتر دبلیو. مک مورای[7]» روشی برای بهینهسازی اسنابرهای مقاومتی – خازنی شرح داده است. نکات برجستهی این روش در زیر آمده است.

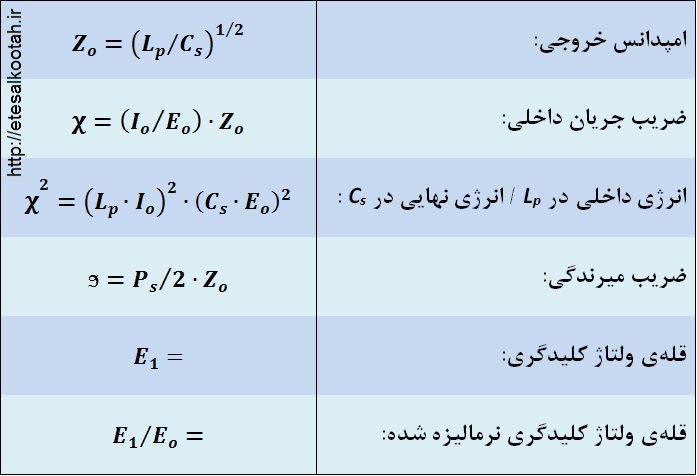

تعاریف زیر مورد استفاده قرار گرفتهاند:

.

.

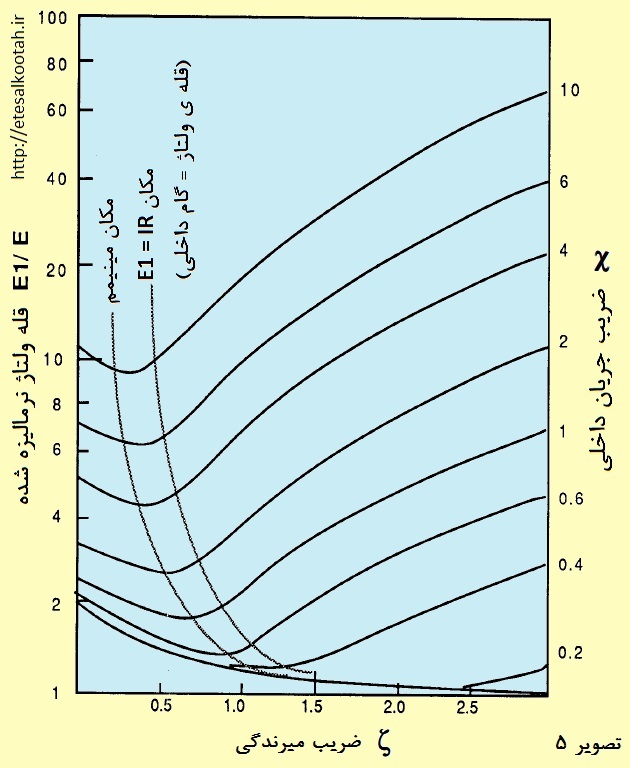

در فرآیند طراحی Io, Eo و Lp فرضهای معلوم هستند و بایستی مقادیر Rs و Cs تعیین شوند، طوری کهیک قلهی ولتاژ قابل قبول (E1) به دست دهند. تصویر 5 رابطه میان E1/Eo و ضریب میرندگی را در مقادیر مختلف ضریب جریان داخلی در اختیار میگذارد. نکتهی کلیدی که این گراف به دست میدهد این است که برای یک ضریب جریان داخلی معین، همیشه یک مقدار بهینهی ضریب میرندگی وجود دارد که پایینترین قلهی ولتاژ را تامین میکند. نکتهی مهم دوم این است که کمترین مقدار قلهی ولتاژ قابل دستیابی توسط اندازهی Cs تعیین میشود. در صورتی که به قلهی ولتاژ کمتری نیاز باشد، بایستی برای این خازن ظرفیت بزرگتری در نظر گرفت. این امر به این معناست که در حالی که قلهی ولتاژ کاهش پیدا میکند، توان تلفاتی بالا میرود.

.

.

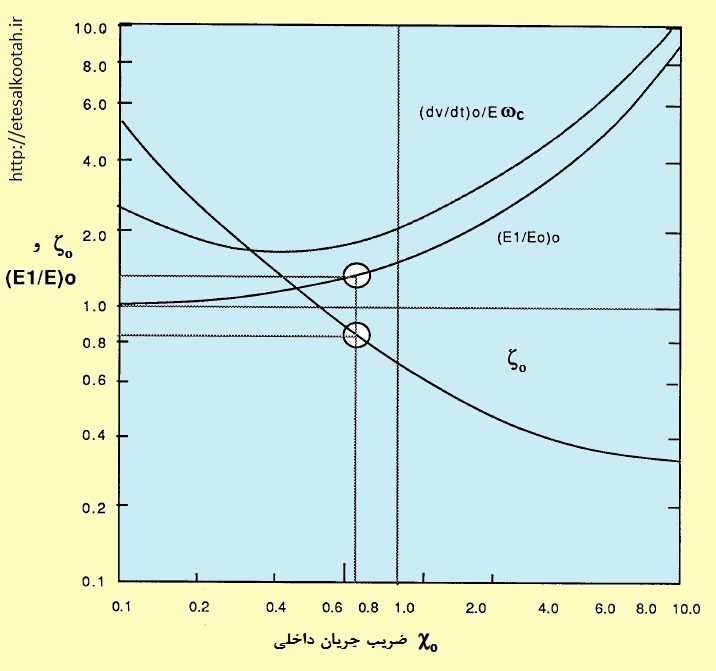

طراحی یک اسنابر مقاومتی – خازنیِ بهینهشده در صورت بهرهگیری از گراف دادهشده در تصویر 6، بسیار آسان است. فرآیند طراحی به صورت گام به گام به شرح زیر است:

1- مقدارهای Io, Eo و Lp تعیین شوند،

2- بیشینهی قلهی ولتاژ انتخاب گردد،

3- نسبت E1/Eo محاسبه شود،

4- از روی گراف تعیین شوند،

5- مقدارهای داده شده برای «ضریب جریان داخلی» و «ضریب میرندگی» برای مقدارهای Rs و Cs محاسبه شوند.

.

.

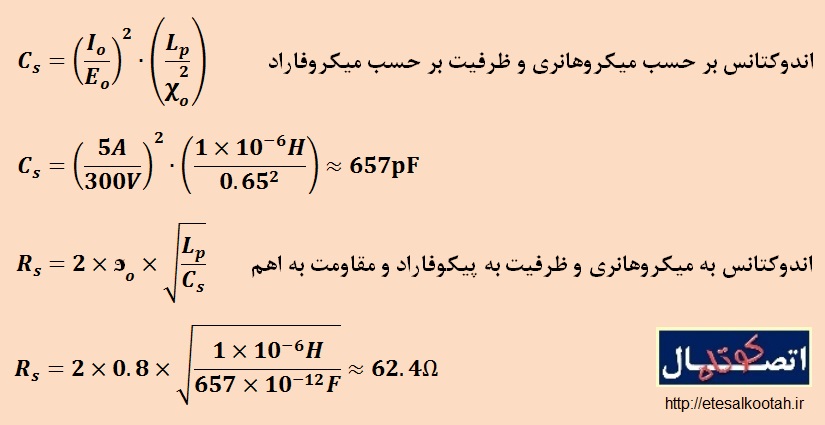

یک مثال واقعی را در اینجا میآوریم: اگر Io = 5A و Eo = 300V و Lp = 1µH و E1 = 400V باشد، پس خواهیم داشت: E1/Eo = 1/33 . با دنبالکردن خط چین و پیکانها روی تصویر بالا مقدار «ضریب جریان داخلی» معادل 0/65 و مقدار «ضریب میرندگی» برابر 0/8 به دست میآید. با داشتن این اطلاعات، مقدارهای Rs و Cs را می توان تعیین کرد:

که برای خازن از یک 680 پیکوفاراد و برای مقاومت از یک 62 اهم استفاده خواهد شد.

در دو گراف بالا ظرفیت خازنی موازی در کلید و زمان انتقال در نظر گرفته نشده است. به طور کلی، مقدار بهینه برای Rs اندکی کمتر از مقدار محاسبه شده خواهد بود. البته، بهینهسازیِ دقیقتر با شبیهسازی عملِ کلیدگری با استفاده از «اسپایس» به دست میآید. این کار با مقادیر محاسبه شده برای Rs آغاز میشود. سپس به سادگی مقدارِ آن به قدری تغییر داده میشود تا مقدار بهینه پیدا شود. در کل، بازهای که این مقدار بهینه در محدودهی آن قرار دارد، آن قدر وسیع هست که بتوان برای Rs با خیال راحت از مقاومتهایی با تولرانس 5% استفاده نمود.

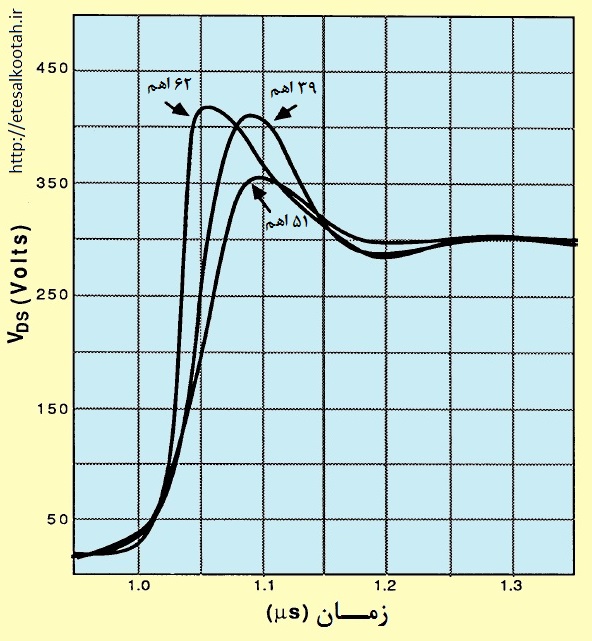

مثالی از بهینهسازی کردن Rs در تصویر زیر نشان داده شده است که در آن یک ماسفت از نوع IRF840 به عنوان کلید به کار رفته است. مقدار بهینه برای مقاومت 51 اهم، و برای E1 ولتاژ 363 ولت است. اگر Rs برابر 39 و یا 62 اهم باشد، ولتاژ E1 بالاتر خواهد بود. به دلیل حضور ظرفیت خازنی موازیِ کلید، قلهی ولتاژ نهایی زیر 400 ولت است. اگر E1 مجاز باشد که به 400 ولت افزایش پیدا کند، ظرفیت خازنی کوچکتری میتواند برای Cs به کار گرفته شود و در نتیجه، مقداری در توان تلفاتی صرفهجویی شود.

.

.

این مثال نشاندهندهی اهمیت شبیهسازی و بهینهسازی در مدارهای اسنابری است که با استفاده از افزارههای مجزا ساخته میشوند. گرافها طراح را وارد میدان بازی میکنند و شبیهسازی به او اجازهی یک بازی خوب را میدهد.

.

تعیین مقدار Lp

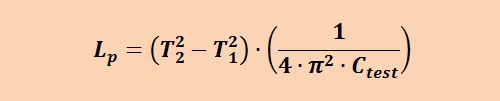

مقدارهای Eo و Io مستقیم از مدار میآیند. برای یافتن مقدار E1 باید به «ندای وجدان[8]» رجوع کرد! این مقدار به ولتاژ نامی[9] کلید و «ضریب تقلیل ولتاژ[10]» آن بستگی دارد. طراح باید «قلهی ولتاژ قابل قبول» را انتخاب کند. همهی این سه کمیت بسیار واضح هستند. البته Lp مشخصهای است که به طراحی چینش افزارهها و فیبر مدار چاپی وابستگی دارد و در واقع به آسانی محاسبهپذیر نمیباشد. مقدار Lp در یک مدار را میتوان با اندازهگیری چرخهی یک دورهی رینگینگ (T1)، و سپس موازیبستن یک خازن با ظرفیت معلوم (Ctest) به کلید، و در پایان با اندازهگیری دوبارهی دوره (T2) تعیین کرد. مقدار Lp از رابطهی زیر پیدا میشود:

به طور معمول ظرفیت خازن تست را در حدود دو برابر ظرفیت کلید در نظر میگیرند.

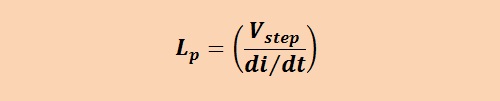

روش دیگر برای تعیین مقدار Lp در مدارهای با توانهای بالاتر، استفاده از «پلهی ولتاژی[11]» (Vstep) است که به خاطر dI/dtی جریانِ عبوری در Lp در زمان وصل بر روی Vce یا Vds پدیدار میشود:

با بسته شدن کلید Cs شارژ میشود. این بدین معناست که به خاطر تخلیهی Cs از طریق Rs، یک «پالس سوزنی جریان[12]» علاوه بر جریان نرمال عبوری، از کلید خواهد گذشت. این یک پالس کوتاه انتقالی است که به سرعت نزول میکند، اما عملاً به جریان وصل افزوده میشود و باید در کار طراحی به حساب آورده شود. یادآور میشود که «اسنابرهای مقاومت – خازن – دیود» نیز، که در بخش بعدی این نوشتار به آنها پرداخته خواهد شد، پالسهای سوزنی جریانِ وصل را دارند، اما این پالسها را میتوان سادهتر کنترل کرد زیرا در آن مدارها لازم نیست که مقدار Rs برای به دست آوردن بیشینهی تضعیفِ دامنه، بهینه سازی شود.

اسنابرهای مقاومت – خازنی برای بهکارگیری در کاربردهای قدرت پایین و قدرت متوسط بسیار سودمند هستند، اما هنگامیکه سطح توان بیش از چند صد وات بشود، تلفات درون اسنابر بسیار زیاد خواهد شد و در چنین مواردی باید به استفاده از انواع دیگرِ اسنابر فکر کرد. البته، اسنابرهای مقاومت – خازنی جایگاه خود را در تجهیزات قدرت بالا به عنوان شبکهی تضعیفکنندهی ثانوی، و مانعی در برابر رینگینگهای فرکانس بالا دارند. در این مصارف، اسنابرهای گفتهشده تلفات انرژی بالایی ایجاد نمیکنند.

.

.

.

مطالب مرتبط:

طراحی «اسنابر» برای حفاظت مدارهای الکترونیک قدرت - بخش 1

طراحی «اسنابر» برای حفاظت مدارهای الکترونیک قدرت - بخش 3

طراحی «اسنابر» برای حفاظت مدارهای الکترونیک قدرت - بخش 4 (بخش پایانی)

.

[1] Ringing

[2] Carbon Composition Resistor[3] Thin-Film Resistor

[4] Wire-Wound Resistor

[5] Self-Inductance

[6] Carbon-Film Resistor

[7] Dr. W. McMurray

.

|

www.etesalkootah.ir || 2017-10-29 © 2015 www.etesalkootah.ir © All rights reserved. تمامی حقوق برای www.etesalkootah.ir محفوظ است. بیان شفاهی بخش یا تمامی یک مطلب از www.etesalkootah.ir در رادیو، تلویزیون و رسانه های مشابه آن با ذکر واضح "اتصال کوتاه دات آی آر" بعنوان منبع مجاز است. هر گونه استفاده کتبی از بخش یا تمامی هر یک از مطالب www.etesalkootah.ir در سایت های اینترنتی در صورت قرار دادن لینک مستقیم و قابل "کلیک" به آن مطلب در www.etesalkootah.ir مجاز بوده و در رسانه های چاپی نیز در صورت چاپ واضح "www.etesalkootah.ir" بعنوان منبع مجاز است. |

.

باوجه به گستردگی شبکه های اجتماعی خواهشمند است چنانچه میسر شود کانال یا گروهی به نام اتصال کوتاه در تلگرام قرار بدهید که خیل کثیر علاقمند بتوانند استفاده از مطالب مفید شما بنمایند.باتشکر